HTTP://WWW.APEXMICROTECH.COM (800) 546-APEX (800) 546-2739

### **FEATURES**

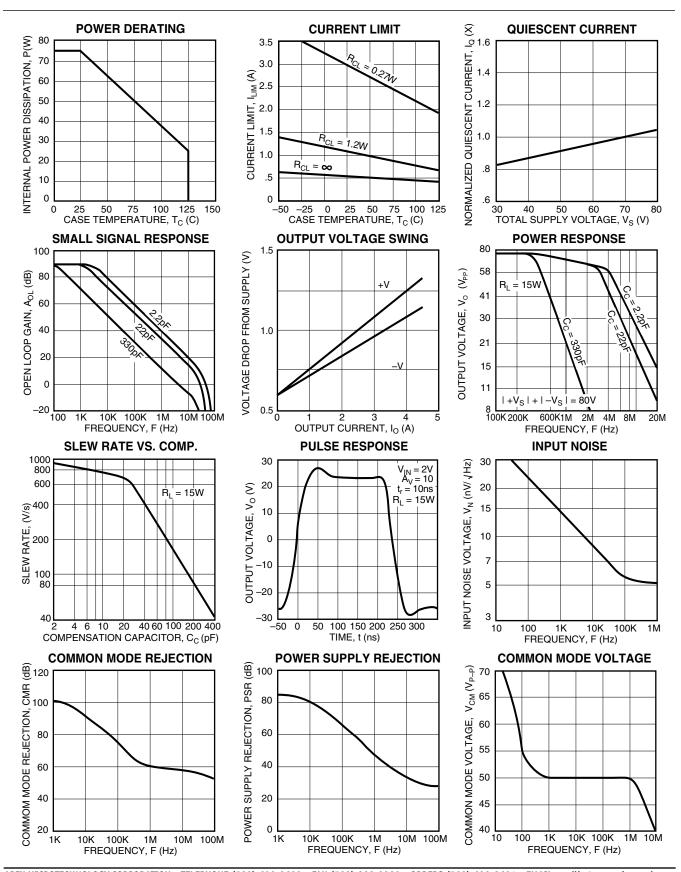

- VERY FAST SLEW RATE 900 V/μs

- POWER MOS TECHNOLOGY 4A peak rating

- LOW INTERNAL LOSSES 0.75V at 2A

- PROTECTED OUTPUT STAGE Thermal Shutoff

- WIDE SUPPLY RANGE ±15V TO ±40V

### **APPLICATIONS**

- VIDEO DISTRIBUTION AND AMPLIFICATION

- HIGH SPEED DEFLECTION CIRCUITS

- POWER TRANSDUCERS UP TO 5 MHz

- MODULATION OF RF POWER STAGES

- POWER LED OR LASER DIODE EXCITATION

### **DESCRIPTION**

The PA119 is a high voltage, high current operational amplifier optimized to drive a variety of loads from DC through the video frequency range. Excellent input accuracy is achieved with a dual monolithic FET input transistor which is cascoded by two high voltage transistors to provide outstanding common mode characteristics. All internal current and voltage levels are referenced to a zener diode biased on by a current source. As a result, the PA119 exhibits superior DC and AC stability over a wide supply and temperature range.

High speed and freedom from second breakdown is assured by a complementary power MOS output stage. For optimum linearity, especially at low levels, the power MOS transistors are biased in a class A/B mode. Thermal shutoff provides full protection against overheating and limits the heatsink requirements to dissipate the internal power losses under normal operating conditions. A built-in current limit of 0.5A can be increased with the addition of two external resistors. Transient inductive load kickback protection is provided by two internal clamping diodes. External phase compensation allows the user maximum flexibility in obtaining the optimum slew rate and gain bandwidth product at all gain settings. A heatsink of proper rating is recommended.

This hybrid circuit utilizes thick film (cermet) resistors, ceramic capacitors, and silicon semiconductor chips to maximize reliability, minimize size, and give top performance. Ultrasonically bonded aluminum wires provide reliable interconnections at all operating temperatures. The 8-pin TO-3 package is hermetically sealed and electrically isolated. The use of compressible thermal washers and/or improper mounting torque will void the product warranty. Please see "General Operating Considerations".

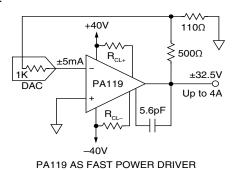

# TYPICAL APPLICATION

8-pin TO-3

PACKAGE STYLE CE

### TYPICAL APPLICATION

This fast power driver utilizes the 900V/µs slew rate of the PA119 and provides a unique interface with a current output DAC. By using the DAC's internal  $1 \text{K}\Omega$  feedback resistor, temperature drift errors are minimized, since the temperature drift coefficients of the internal current source and the internal feedback resistor of the DAC are closely matched. Gain of  $V_{\text{OUT}}$  to  $I_{\text{IN}}$  is –6.5/mA. The DAC's internal 1K resistor together with the external  $500\Omega$  and  $110\Omega$  form a "tee network" in the feedback path around the PA119. This effective resistance equals  $6.5 \text{K}\Omega$ . Therefore the entire circuit can be modeled as  $6.5 \text{K}\Omega$  feedback resistor from output to inverting input and a 5mA current source into the inverting input of the PA119. Now we see the familiar current to voltage conversion for a DAC where  $V_{\text{OUT}}$  =  $-I_{\text{IN}}$  x  $R_{\text{FEEDBACK}}$ .

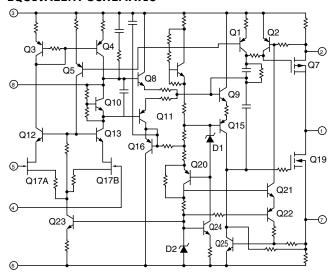

### **EQUIVALENT SCHEMATIC**

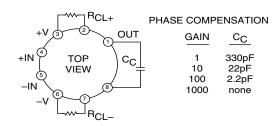

### **EXTERNAL CONNECTIONS**

# ABSOLUTE MAXIMUM RATINGS SPECIFICATIONS

## **PA119CE • PA119CEA**

### ABSOLUTE MAXIMUM RATINGS

SUPPLY VOLTAGE,  $+V_s$  to  $-V_s$ 80V OUTPUT CURRENT, within SOA 5A POWER DISSIPATION, internal 75W INPUT VOLTAGE, differential 40V INPUT VOLTAGE, common mode ±٧٥ 300°C TEMPERATURE, pin solder — 10 sec TEMPERATURE, junction<sup>1</sup> TEMPERATURE, storage 175°C -65 to 150°C OPERATING TEMPERATURE RANGE, case -55 to 125°C

### **SPECIFICATIONS**

|                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | PA119                                                          |                                                                                            |                        | PA119A      |                                       |                        |                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------------------------------------------|------------------------|-------------|---------------------------------------|------------------------|------------------------------------------------------------------|

| PARAMETER                                                                                                                                                                                                                                                                                        | TEST CONDITIONS <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | MIN                                                            | TYP                                                                                        | MAX                    | MIN         | TYP                                   | MAX                    | UNITS                                                            |

| INPUT OFFSET VOLTAGE, initial OFFSET VOLTAGE, vs. temperature OFFSET VOLTAGE, vs. supply OFFSET VOLTAGE, vs. power BIAS CURRENT, initial BIAS CURRENT, vs. supply OFFSET CURRENT, initial INPUT IMPEDANCE, DC INPUT CAPACITANCE COMMON MODE VOLTAGE RANGE <sup>3</sup> COMMON MODE REJECTION, DC | $T_{c} = 25^{\circ}\text{C}$ $T_{c} = 25^{\circ}\text{C}$ to +85°C $T_{c} = 25^{\circ}\text{C}$ to +85°C $T_{c} = 25^{\circ}\text{C}$ to +85°C $T_{c} = 25^{\circ}\text{C}$ $T_{c} = 25^{\circ}\text{C}$ $T_{c} = 25^{\circ}\text{C}$ | ±V <sub>s</sub> -15                                            | ±.5<br>10<br>10<br>20<br>10<br>.01<br>5<br>10 <sup>11</sup><br>6<br>±V <sub>s</sub> -12    | ±3<br>30<br>200<br>100 | *           | ±.35 5 * * 5 * 3 * *                  | ±.75<br>15<br>50<br>25 | mV<br>μV/°C<br>μV/V<br>μV/W<br>pA<br>pA/V<br>pA<br>MΩ<br>pF<br>V |

| <b>GAIN</b> OPEN LOOP GAIN at 10Hz OPEN LOOP GAIN at 10Hz GAIN BANDWIDTH PRODUCT at 1MHz POWER BANDWIDTH, $A_V = 100$ POWER BANDWIDTH, $A_V = 1$                                                                                                                                                 | $T_c = 25^{\circ}C$ , $R_L = 1K\Omega$<br>$T_C = 25^{\circ}C$ , $R_L = 15\Omega$                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 74                                                             | 111<br>88<br>100<br>3.5<br>250                                                             |                        | *           | * * * *                               |                        | dB<br>dB<br>MHz<br>MHz<br>kHz                                    |

| OUTPUT VOLTAGE SWING³ VOLTAGE SWING³ VOLTAGE SWING³ SETTLING TIME to .1% SETTLING TIME to .01% SLEW RATE, $A_V = 100$ SLEW RATE, $A_V = 100$                                                                                                                                                     | $\begin{split} & T_c = 25^{\circ}\text{C}, I_o = 4\text{A} \\ & T_c = 25^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, I_o = 2\text{A} \\ & T_c = 25^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, I_o = 78\text{mA} \\ & T_c = 25^{\circ}\text{C}, 2\text{V step} \\ & T_c = 25^{\circ}\text{C}, 2\text{V step} \\ & T_c = 25^{\circ}\text{C}, C_c = 2.2\text{pF} \\ & T_c = 25^{\circ}\text{C}, C_c = 22\text{pF} \end{split}$                                                                                                  | ±V <sub>s</sub> -5<br>±V <sub>s</sub> -3<br>±V <sub>s</sub> -1 | ±V <sub>s</sub> -1.5<br>±V <sub>s</sub> 75<br>±V <sub>s</sub> 5<br>.3<br>1.2<br>900<br>650 |                        | *<br>*<br>* | *     *     *     *     *     *     * |                        | V<br>V<br>V<br>µs<br>µs<br>V/µs                                  |

| POWER SUPPLY<br>VOLTAGE<br>CURRENT, quiescent                                                                                                                                                                                                                                                    | T <sub>c</sub> = 25°C to +85°C<br>T <sub>c</sub> = 25°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ±15                                                            | ±35<br>100                                                                                 | ±40<br>120             | *           | *                                     | *                      | V<br>mA                                                          |

| THERMAL RESISTANCE, AC, junction to case <sup>4</sup> RESISTANCE, DC, junction to case RESISTANCE, junction to air TEMPERATURE RANGE, case                                                                                                                                                       | $T_c$ = 25°C to +85°C, F > 60Hz<br>$T_c$ = 25°C to +85°C, F < 60Hz<br>$T_c$ = 25°C to +85°C<br>Meets full range specifications                                                                                                                                                                                                                                                                                                                                                                                                          | _25                                                            | 1.46<br>1.84<br>30                                                                         | 1.64<br>2.0<br>+85     | *           | * *                                   | * *                    | °C/W<br>°C/W<br>°C/W<br>°C                                       |

NOTES: \*

- \* The specification of PA119A is identical to the specification for PA119 in applicable column to the left.

- 1. Long term operation at the maximum junction temperature will result in reduced product life. Derate internal power dissipation to achieve high MTTF.

- 2. The power supply voltage for all specifications is the TYP rating unless noted as a test condition.

- 3.  $+V_s$  and  $-V_s$  denote the positive and negative supply rail respectively. Total  $V_s$  is measured from  $+V_s$  to  $-V_s$ .

- 4. Rating applies if the output current alternates between both output transistors at a rate faster than 60Hz.

**CAUTION**

The internal substrate contains beryllia (BeO). Do not break the seal. If accidentally broken, do not crush, machine, or subject to temperatures in excess of 850°C to avoid generating toxic fumes.

#### **GENERAL**

Please read Application Note 1 "General Operating Considerations" which covers stability, supplies, heat sinking, mounting, current limit, SOA interpretation, and specification interpretation. Visit www.apexmicrotech.com for design tools that help automate tasks such as calculations for stability, internal power dissipation, current limit; heat sink selection; Apex's complete Application Notes library; Technical Seminar Workbook; and Evaluation Kits.

### **CURRENT LIMIT**

Q2 (and Q25) limit output current by turning on and removing gate drive when voltage on pin 2 (pin 7) exceeds .65V differential from the positive (negative) supply rail. With internal resistors equal to  $1.2\Omega$ , current limits are approximately 0.5A with no external current limit resistors. With the addition of external resistors current limit will be:

$$I_{LIM} = \frac{.65V}{R_{CL}} + .54A$$

To determine values of external current limit resistors:

$$R_{CL} = \frac{.65V}{I_{CL} - .54A}$$

### PHASE COMPENSATION

At low gain settings, an external compensation capacitor is required to insure stability. In addition to the resistive feedback network, roll off or integrating capacitors must also be considered when determining gain settings. The capacitance values listed in the external connection diagram, along with good high frequency layout practice, will insure stability. Interpolate values for intermediate gain settings.

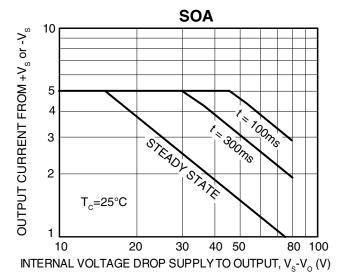

### SAFE OPERATING AREA (SOA)

The MOSFET output stage of this power operational amplifier has two distinct limitations:

- The current handling capability of the MOSFET geometry and the wire bonds.

- 2. The junction temperature of the output MOSFETs.

The SOA curves combine the effect of these limits and allow for internal thermal delays. For a given application, the direction and magnitude of the output current should be calculated or measured and checked against the SOA curves. This is simple for resistive loads but more complex for reactive and EMF generating loads. The following guidelines may save extensive analytical efforts:

Capacitive and inductive loads up to the following maximums are safe:

| $\pm V_{_{\mathrm{S}}}$ | CAPACITIVE LOAD | INDUCTIVE LOAD |

|-------------------------|-----------------|----------------|

| 40V                     | .1μF            | 11mH           |

| 30V                     | 500μF           | 24mH           |

| 20V                     | 2500μF          | 75mH           |

| 15V                     | ∞               | 100mH          |

- Safe short circuit combinations of voltage and current are limited to a power level of 100W.

- The output stage is protected against transient flyback. However, for protection against sustained, high energy flyback, external fast-recovery diodes should be used.

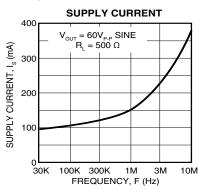

### SUPPLY CURRENT

The PA119 features a class A/B driver stage to charge and discharge gate capacitance of Q7 and Q19. As these currents approach 0.5A, the savings of quiescent current over that of a class A driver stage is considerable. However, supply current drawn by the PA119, even with no load, varies with slew rate of the output signal as shown below.

### **OUTPUT LEADS**

Keep the output leads as short as possible. In the video frequency range, even a few inches of wire have significant inductances, raising the interconnection impedance and limiting the output current slew rate. Furthermore, the skin effect increases the resistance of heavy wires at high frequencies. Multistrand Litz Wire is recommended to carry large video currents with low losses.

### THERMAL SHUTDOWN

The thermal protection circuit shuts off the amplifier when the substrate temperature exceeds approximately 150°C. This allows the heatsink selection to be based on normal operating conditions while protecting the amplifier against excessive junction temperature during temporary fault conditions.

Thermal protection is a fairly slow-acting circuit and therefore does not protect the amplifier against transient SOA violations (areas outside of the steady state boundary). It is designed to protect against short-term fault conditions that result in high power dissipation within the amplifier. If the conditions that cause thermal shutdown are not removed, the amplifier will oscillate in and out of shutdown. This will result in high peak power stresses, destroy signal integrity, and reduce the reliability of the device.

### **STABILITY**

Due to its large bandwidth, the PA119 is more likely to oscillate than lower bandwidth power operational amplifiers. To prevent oscillations a reasonable phrase margin must be maintained by:

- Selection of the proper phase compensation capacitor. Use the values given in the table under external connections and interpolate if necessary. The phase margin can be increased by using a larger capacitor at the expense of slew rate. Total physical length (pins of the PA119, capacitor leads plus printed circuit traces) should be limited to a maximum of 3.5 inches.

- 2. Keep the external sumpoint stray capacitance to ground at a minimum and the sumpoint load resistance (input and feedback resistors in parallel) below  $500\Omega$ . Larger sumpoint load resistances can be used with increased phase compensation and/or by bypassing the feedback resistor.

- 3. Connect the case to any AC ground potential.